64-point FFT/IFFT Processor for WLAN 802.11a in VHDL

Year: 2015

Expertise: VLSI Design, Communication System

Outcome: Synthesizable VHDL, Functional and Timing Simulation Report, Implementation Report

Implementation of 64-point FFT/IFFT Processor for Wireless LAN 802.11a Application in a Synthesizable VHDL.

Bagus Hanindhito

Department of Electrical Engineering, School of Electrical Engineering and Informatics

Institut Teknologi Bandung, Indonesia

Email : hanindhito@bagus.my.id

Abstract—The project objective is to implement a design of 64-point FFT/IFFT processor for Wireless LAN 802.11a application in a synthesizable VHDL. For this application, one Fast-Fourier Transform (FFT) operation has to be completed at around 4μs. Conventional Cooley-Tukey which uses radix-2 FFT algorithm requires 192 complex butterfly operations to compute 64-point FFT/IFFT. The butterfly structure must be clocked at 48Mhz to achieve the maximum time of computation for single FFT/IFFT operation. It consumes 0.18mm2 area in IHP 0.25μm technology and dissipates 17mW of power which is quite high for mobile application.

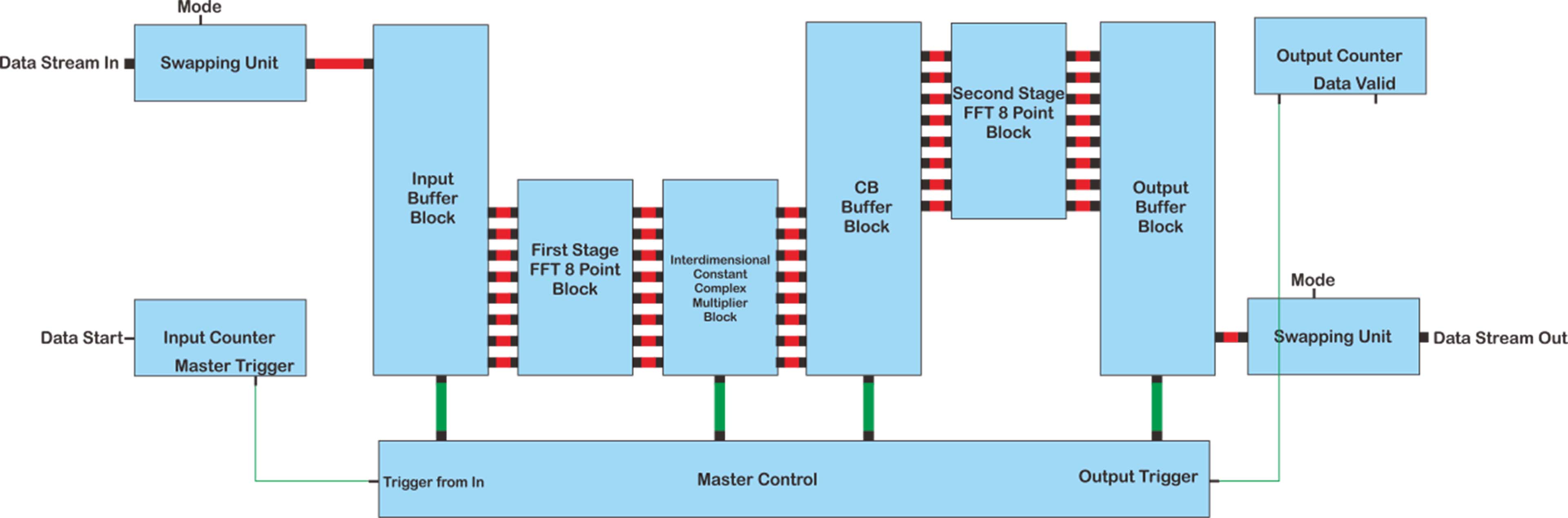

I decided to implement a novel fixed-point 16-bit word-width 64-point FFT/IFFT processor designed by Koushik Maharatna, Eckhard Grass, and Ulrich Jagdhold. This FFT/IFFT processor developed primarily for the application in IEEE 802.11a wireless LAN processor which utilizes OFDM. It uses the two-dimensional structure of 8-point FFTs to realize the 64-point FFTs structure. At the end of the project, I implemented in a synthesizable VHDL. The synthesis was done in Altera® Cyclone® II EP2C70F896C6 FPGA device using Altera® Quartus® II 9.1sp2. The implementation showed that it could compute one FFT/IFFT operation in 1.6μs.

Index Terms— ATLAS Insertable B-Layer, Back-of-Crate Module, Data Acquisition System, Low-Level Test, Read-Out-Driver Module.

FFT-IFFT 64-point processor High Level Diagram

FFT-IFFT 64-point processor simulation waveform

0 Comments